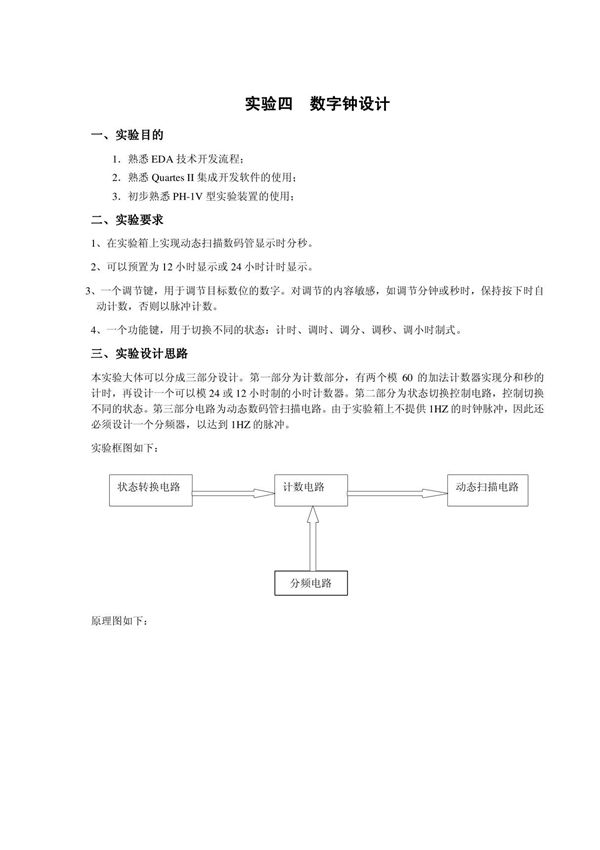

EDA数字钟设计是一种基于电子设计自动化(EDA)工具的数字时钟电路实现方案。该设计利用硬件描述语言(如VHDL或Verilog)进行建模和仿真,通过逻辑综合、布局布线等步骤生成可在FPGA或ASIC上实现的电路。设计包含时钟信号产生、时间计数、显示驱动等核心模块,具有可编程、高精度和低功耗等特点。该精品设计方案注重优化电路结构和时序约束,确保在资源占用和性能之间达到最佳平衡,同时提供完善的功能验证和测试方案。

EDA数字钟设计是一种基于电子设计自动化(EDA)工具的数字时钟电路实现方案。该设计利用硬件描述语言(如VHDL或Verilog)进行建模和仿真,通过逻辑综合、布局布线等步骤生成可在FPGA或ASIC上实现的电路。设计包含时钟信号产生、时间计数、显示驱动等核心模块,具有可编程、高精度和低功耗等特点。该精品设计方案注重优化电路结构和时序约束,确保在资源占用和性能之间达到最佳平衡,同时提供完善的功能验证和测试方案。