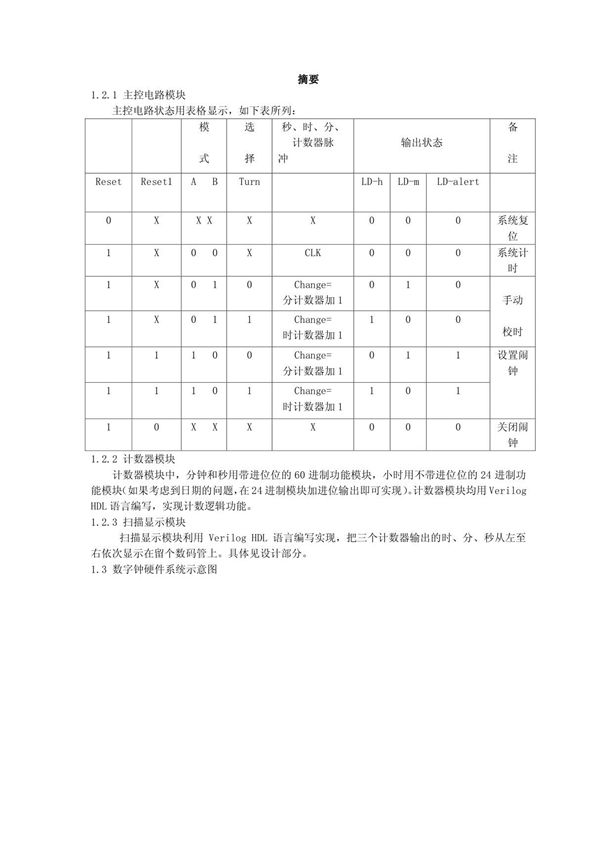

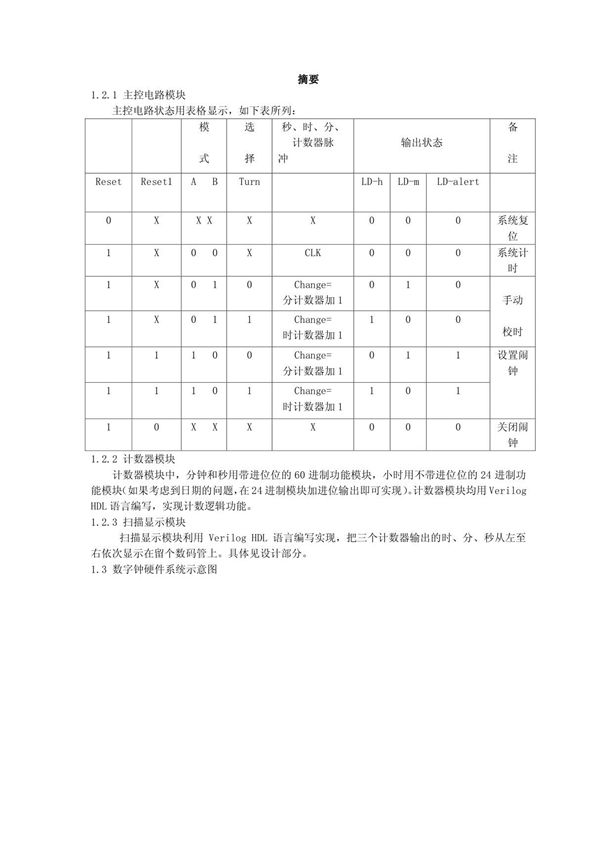

基于EDA设计数字钟是一种利用电子设计自动化工具进行数字电路设计与仿真的方法。该设计通常包括计时模块、显示模块和控制模块,通过EDA软件(如Multisim、Proteus或QuartusII)完成原理图绘制、逻辑仿真和PCB布局。设计过程中需考虑时钟信号稳定性、显示驱动电路优化以及按键消抖等功能实现,最终通过FPGA或单片机硬件平台验证。该方案具有设计周期短、可修改性强、仿真直观等优势,适合教学与工程实践。

基于EDA设计数字钟是一种利用电子设计自动化工具进行数字电路设计与仿真的方法。该设计通常包括计时模块、显示模块和控制模块,通过EDA软件(如Multisim、Proteus或QuartusII)完成原理图绘制、逻辑仿真和PCB布局。设计过程中需考虑时钟信号稳定性、显示驱动电路优化以及按键消抖等功能实现,最终通过FPGA或单片机硬件平台验证。该方案具有设计周期短、可修改性强、仿真直观等优势,适合教学与工程实践。