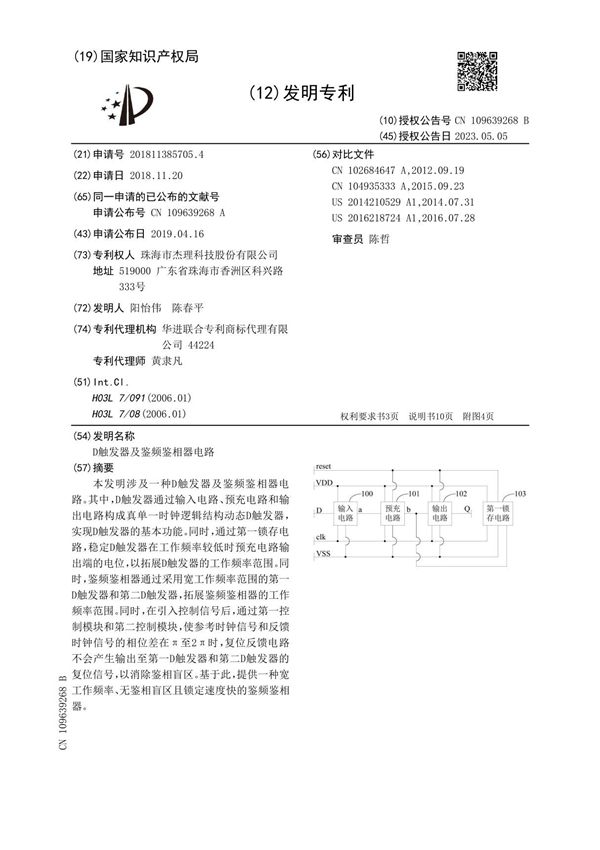

D触发器(DFlip-Flop)是一种基本的数字电路元件,用于存储单个二进制位(0或1)。它在时钟信号的边沿(上升沿或下降沿)触发,将输入数据(D端)的值传递到输出端(Q端),并在时钟边沿之后保持该值不变,直到下一个时钟边沿到来。D触发器广泛应用于寄存器、计数器、状态机等数字系统中,是时序电路的核心组件之一。鉴频鉴相器(Phase-FrequencyDetector,PFD)是一种用于锁相环(PLL)和时钟数据恢复(CDR)电路的关键模块。它的功能是检测输入信号与参考信号之间的相位差和频率差,并输出相应的误差信号(通常为UP和DOWN脉冲)。PFD通过比较两个信号的边沿,产生控制信号来调整压控振荡器(VCO)的频率,最终使输入信号与参考信号同步。鉴频鉴相器在高精度时钟合成、通信系统和数据同步中具有重要作用。