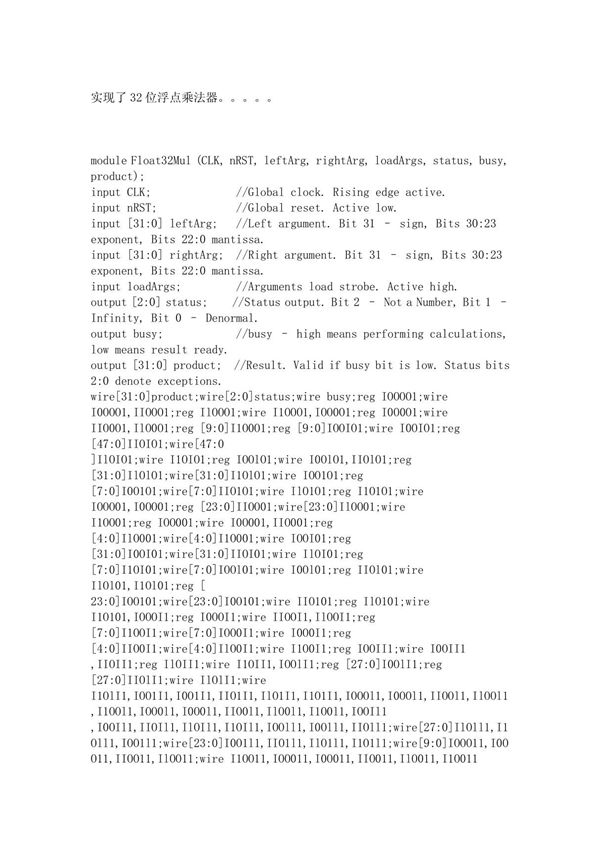

这段简介介绍了32位浮点乘法器的Verilog实现:32位浮点乘法器是一种基于IEEE754标准的数字电路设计,使用Verilog硬件描述语言实现。该乘法器能够执行单精度(32位)浮点数的乘法运算,包含符号位处理、指数相加和尾数相乘三个主要部分。设计采用流水线结构提高吞吐量,支持标准浮点数的规格化处理、非规格化数处理以及特殊值(如NaN和无穷大)的检测。实现中考虑了面积优化和时序约束,可综合到FPGA或ASIC平台。该模块通常包含输入寄存器、乘法运算单元、结果规格化单元和输出寄存器,适用于高性能计算、DSP处理器和图形处理等需要浮点运算的应用场景。