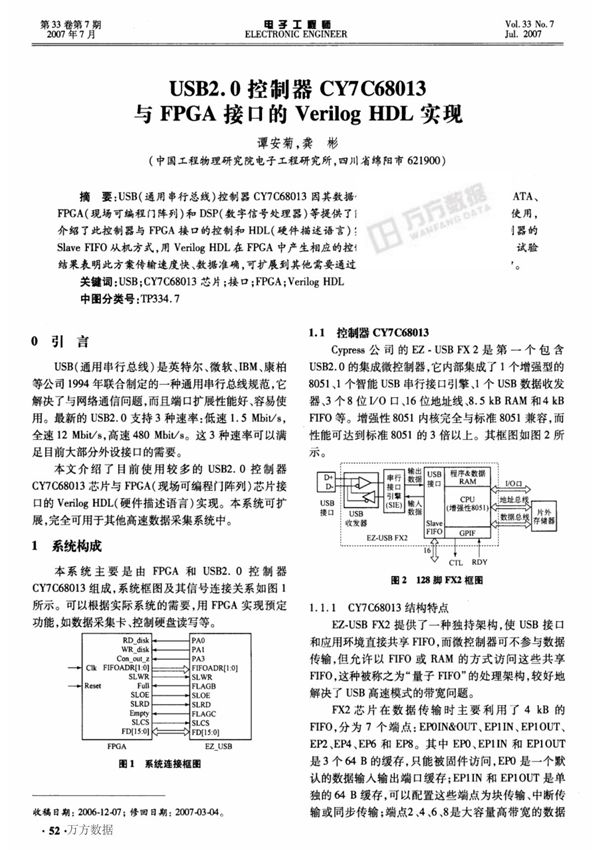

USB2.0控制器CY7C68013与FPGA接口的VerilogHDL实现简介CY7C68013是Cypress公司推出的一款高速USB2.0控制器,支持全速(12Mbps)和高速(480Mbps)模式。它通常用于需要高速数据传输的嵌入式系统中。在FPGA中,通过VerilogHDL实现与CY7C68013的接口,主要涉及以下几个关键部分:1.**GPIF(GeneralProgrammableInterface)模式配置**:CY7C68013支持可编程接口(GPIF),允许用户自定义时序和控制信号,以适应不同的FPGA或处理器接口需求。2.**FIFO接口**:CY7C68013通常通过FIFO(先入先出缓冲区)与FPGA进行数据交换。FPGA需要实现读写逻辑,包括FIFO选择(如IFCLK、FD[15:0]、SLWR、SLRD、FIFOADR等信号的控制)。3.**时钟同步**:FPGA需要根据CY7C68013提供的IFCLK(接口时钟)进行数据同步,确保数据传输的稳定性。4.**状态机设计**:FPGA通常使用有限状态机(FSM)来管理USB数据传输流程,包括初始化、数据发送、数据接收以及错误处理等状态。5.**数据传输协议**:根据应用需求,FPGA可能需要实现自定义协议(如批量传输、中断传输或同步传输),以确保数据正确解析和封装。通过合理的VerilogHDL代码设计,FPGA可以高效地与CY7C68013通信,实现高速USB2.0数据传输,适用于数据采集、工业控制、通信设备等应用场景。