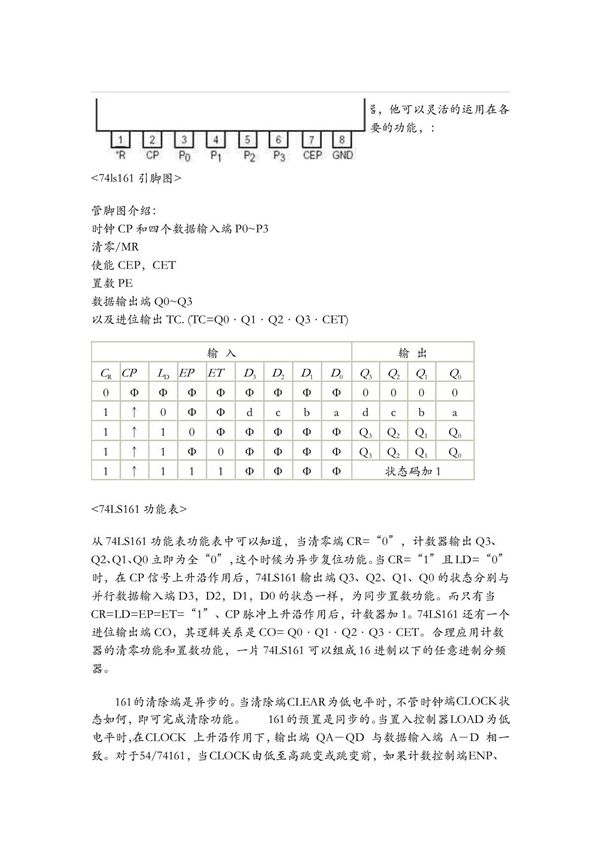

74LS161是一种常用的4位二进制同步计数器集成电路,属于TTL逻辑系列。它具有同步预置、异步清零和计数使能功能,广泛应用于数字电路设计中。**引脚图概述**:74LS161采用16引脚DIP封装,主要引脚包括时钟输入(CLK)、数据输入(D0-D3)、预置使能(LOAD)、清零(CLR)、计数使能(ENP、ENT)以及进位输出(RCO)。**管脚功能表**:1.**CLK**(引脚2):时钟输入,上升沿触发计数或预置操作。2.**CLR**(引脚1):异步清零(低电平有效),强制计数器归零。3.**LOAD**(引脚9):同步预置使能(低电平有效),加载D0-D3数据到计数器。4.**ENP、ENT**(引脚7、10):计数使能端(高电平有效),两者均为高时允许计数。5.**D0-D3**(引脚3-6):并行数据输入,用于预置计数初值。6.**Q0-Q3**(引脚11-14):计数器输出,反映当前计数值。7.**RCO**(引脚15):进位输出,当计数器达到最大值(1111)时输出高电平。74LS161适用于频率分频、时序控制等应用,是数字电路设计中的基础元件之一。